# ARM Generic Interrupt Controller

**Architecture version 2.0**

**Architecture Specification**

# **ARM Generic Interrupt Controller**

Copyright © 2008, 2011, 2013 ARM. All rights reserved.

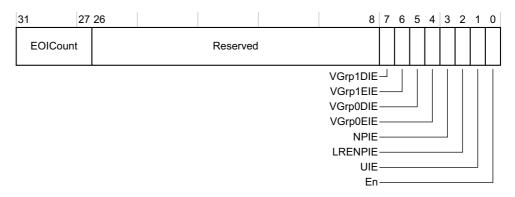

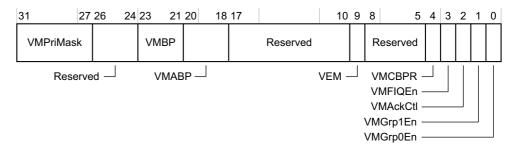

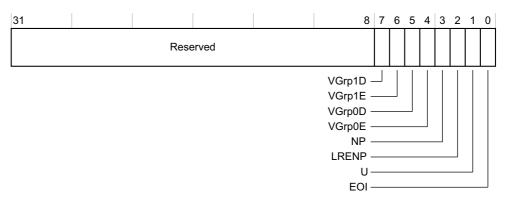

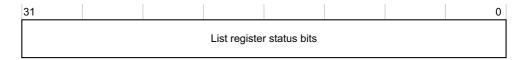

#### **Release Information**

The following changes have been made to this document.

#### **Change History**

| Date Issue Co     |     | Confidentiality  | Change                                            |

|-------------------|-----|------------------|---------------------------------------------------|

| 23 September 2008 | A   | Non-Confidential | First release for version 1.0                     |

| 13 June 2011      | В   | Non-Confidential | First release for version 2.0                     |

| 26 July 2013      | B.b | Non-Confidential | Re-release of issue B with new Proprietary Notice |

#### Status of Issue B.b of this document

Issue B.b of this document is a re-issue of issue B incorporating the updated Propriatary Notice for the document. Beyond page four of the document the only changes between issue B and issue B.b are:

- Changes to the page footers to show the new version number, copyright dates, and ID code.

- Changed page numbering, because of the longer Propriatary Notice.

- A statement in Appendix C Revisions that there are no technical changes between issue B and issue B.b.

#### **Proprietary Notice**

ARM GENERIC INTERRUPT CONTROLLER (GIC) ARCHITECTURE SPECIFICATION LICENCE

THIS END USER LICENCE AGREEMENT ("LICENCE") IS A LEGAL AGREEMENT BETWEEN YOU (EITHER A SINGLE INDIVIDUAL, OR SINGLE LEGAL ENTITY) AND ARM LIMITED ("ARM") FOR THE USE OF THE RELEVANT GIC ARCHITECTURE SPECIFICATION ACCOMPANYING THIS LICENCE. ARM IS ONLY WILLING TO LICENSE THE RELEVANT GIC ARCHITECTURE SPECIFICATION TO YOU ON CONDITION THAT YOU ACCEPT ALL OF THE TERMS IN THIS LICENCE. BY CLICKING "I AGREE" OR OTHERWISE USING OR COPYING THE RELEVANT GIC ARCHITECTURE SPECIFICATION YOU INDICATE THAT YOU AGREE TO BE BOUND BY ALL THE TERMS OF THIS LICENCE. IF YOU DO NOT AGREE TO THE TERMS OF THIS LICENCE, ARM IS UNWILLING TO LICENSE THE RELEVANT GIC ARCHITECTURE SPECIFICATION TO YOU AND YOU MAY NOT USE OR COPY THE RELEVANT GIC ARCHITECTURE SPECIFICATION AND YOU SHOULD PROMPTLY RETURN THE RELEVANT GIC ARCHITECTURE SPECIFICATION TO ARM.

"LICENSEE" means You and your Subsidiaries.

"Subsidiary" means, if You are a single entity, any company the majority of whose voting shares is now or hereafter owned or controlled, directly or indirectly, by You. A company shall be a Subsidiary only for the period during which such control exists.

- Subject to the provisions of Clauses 2, 3 and 4, ARM hereby grants to LICENSEE a perpetual, non-exclusive, non-transferable, royalty free, worldwide licence to:

- a. use and copy the relevant GIC Architecture Specification for the purpose of developing and having developed products that comply with the relevant GIC Architecture Specification;

- b. manufacture and have manufactured products which either: (i) have been created by or for LICENSEE under the licence granted in Clause 1a; or (ii) incorporate a product(s) which has been created by a third party(s) under a licence granted by ARM in Clause 1a of such third party's ARM GIC Architecture Specification Licence; and

- c. offer to sell, sell, supply or otherwise distribute products which have either been (i) created by or for LICENSEE under the licence granted in Clause 1a; or (ii) manufactured by or for LICENSEE under the licence granted in Clause 1b.

- 2. LICENSEE hereby agrees that the licence granted in Clause 1 is subject to the following restrictions:

- a. where a product is created under Clause 1a or manufactured under Clause 1b it must contain at least one processor core which has either been (i) developed by or for ARM; or (ii) developed under licence from ARM;

- b. the licences granted in Clause 1c shall not extend to any portion or function of a product that is not itself compliant with part of the relevant GIC Architecture Specification; and

- c. no right is granted to LICENSEE to sublicense the rights granted to LICENSEE under this Agreement.

- 3. Except as specifically licensed in accordance with Clause 1, LICENSEE acquires no right, title or interest in any ARM technology or any intellectual property embodied therein. In no event shall the licences granted in accordance with Clause 1 be construed as granting LICENSEE, expressly or by implication, estoppel or otherwise, a licence to use any ARM technology except the relevant GIC Architecture Specification.

- 4. THE RELEVANT GIC ARCHITECTURE SPECIFICATION IS PROVIDED "AS IS" WITH NO WARRANTIES EXPRESS, IMPLIED OR STATUTORY, INCLUDING BUT NOT LIMITED TO ANY WARRANTY OF SATISFACTORY QUALITY, MERCHANTABILITY, NONINFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE.

- No licence, express, implied or otherwise, is granted to LICENSEE, under the provisions of Clause 1, to use the ARM tradename in connection with the relevant GIC Architecture Specification or any products based thereon. Nothing in Clause 1 shall be construed as authority for LICENSEE to make any representations on behalf of ARM in respect of the relevant GIC Architecture Specification.

- 6. This Licence shall remain in force until terminated by you or by ARM. Without prejudice to any of its other rights if LICENSEE is in breach of any of the terms and conditions of this Licence then ARM may terminate this Licence immediately upon giving written notice to You. You may terminate this Licence at any time. Upon expiry or termination of this Licence by You or by ARM LICENSEE shall stop using the relevant GIC Architecture Specification and destroy all copies of the relevant GIC Architecture Specification in your possession together with all documentation and related materials. Upon expiry or termination of this Licence, the provisions of clauses 6 and 7 shall survive.

- 7. The validity, construction and performance of this Agreement shall be governed by English Law.

ARM contract references: LES-PRE-20079 ARM GENERIC INTERRUPT CONTROLLER (GIC) ARCHITECTURE Specification Licence.

| Where the term ARM is used it means "ARM or any of its subsidiaries as appropriate".                                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note                                                                                                                                                                                     |

| The term ARM can refer to versions of the ARM architecture, for example ARMv6 refers to version 6 of the ARM architecture. The context makes it clear when the term is used in this way. |

# Contents

# **ARM Generic Interrupt Controller Architecture Specification**

|           | Pref  | ace                                                         |      |

|-----------|-------|-------------------------------------------------------------|------|

|           |       | About this specification                                    | vi   |

|           |       | Using this specification                                    |      |

|           |       | Conventions                                                 |      |

|           |       | Additional reading                                          |      |

|           |       | Feedback                                                    |      |

| Chapter 1 | Intro | oduction                                                    |      |

| •         | 1.1   | About the Generic Interrupt Controller architecture         | 1-14 |

|           | 1.2   | Security Extensions support                                 |      |

|           | 1.3   | Virtualization support                                      |      |

|           | 1.4   | Terminology                                                 |      |

| Chapter 2 | GIC   | Partitioning                                                |      |

| •         | 2.1   | About GIC partitioning                                      | 2-2  |

|           | 2.2   | The Distributor                                             |      |

|           | 2.3   | CPU interfaces                                              |      |

| Chapter 3 | Inter | rrupt Handling and Prioritization                           |      |

|           | 3.1   | About interrupt handling and prioritization                 | 3-3  |

|           | 3.2   | General handling of interrupts                              |      |

|           | 3.3   | Interrupt prioritization                                    |      |

|           | 3.4   | The effect of interrupt grouping on interrupt handling      |      |

|           | 3.5   | Interrupt grouping and interrupt prioritization             |      |

|           | 3.6   | Additional features of the GIC Security Extensions          |      |

|           | 3.7   | Pseudocode details of interrupt handling and prioritization |      |

|           |       |                                                             |      |

| 3.8   | The effect of the Virtualization Extensions on interrupt handling                           | 3-67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.9   | Example GIC usage models                                                                    | 3-68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Prog  | rammers' Model                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4.1   |                                                                                             | 4-74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4.2   |                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4.3   | , , ,                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4.4   |                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4.5   |                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| GIC S | Support for Virtualization                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5.1   | • •                                                                                         | 5-158                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|       |                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| -     | • •                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|       | •                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5.5   |                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Pseu  | idocode Index                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| A.1   |                                                                                             | A-198                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Regi  | ster Names                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| B.1   |                                                                                             | B-202                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| B.2   |                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| B.3   |                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Revi  | sions                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Glos  | sary                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|       | 3.9  Prog 4.1 4.2 4.3 4.4 4.5  GIC 9 5.1 5.2 5.3 5.4 5.5  Pseu A.1  Regi B.1 B.2 B.3  Revis | Programmers' Model  4.1 About the programmers' model  4.2 Effect of the GIC Security Extensions on the programmers' model  4.3 Distributor register descriptions  4.4 CPU interface register descriptions  4.5 Preserving and restoring GIC state  GIC Support for Virtualization  5.1 About implementing a GIC in a system with processor virtualization  5.2 Managing the GIC virtual CPU interface  5.3 GIC virtual interface control registers  5.4 The virtual CPU interface  5.5 GIC virtual CPU interface registers  Pseudocode Index  A.1 Index of pseudocode functions  Register Names  B.1 Alternative register names  B.2 Register name aliases |

# **Preface**

This preface introduces the *ARM® Generic Interrupt Controller Architecture Specification*. It contains the following sections:

- About this specification on page viii

- Using this specification on page ix

- Conventions on page x

- Additional reading on page xi

- Feedback on page xii.

# About this specification

This specification describes the ARM Generic Interrupt Controller (GIC) architecture.

Throughout this document, references to *the GIC* or *a GIC* refer to a device that implements this GIC architecture. Unless the context makes it clear that a reference is to an IMPLEMENTATION DEFINED feature of the device, these references describe the requirements of this specification.

#### Intended audience

The specification is written for users that want to design, implement, or program the GIC in a range of ARM-compliant implementations from simple uniprocessor implementations to complex multiprocessor systems.

The specification assumes that users have some experience of ARM products. It does not assume experience of the GIC.

# Using this specification

This specification is organized into the following chapters:

#### **Chapter 1** Introduction

Read this for an overview of the GIC, and information about the terminology used in this document.

#### Chapter 2 GIC Partitioning

Read this for a description of the major interfaces and components of the GIC. The chapter also introduces how they operate, in a simple implementation.

#### Chapter 3 Interrupt Handling and Prioritization

Read this for a description of the requirements for interrupt handling, and the interrupt priority scheme for a GIC.

# Chapter 4 Programmers' Model

Read this for a description of the Distributor and CPU interface registers.

#### **Chapter 5** GIC Support for Virtualization

Read this for a description of how the GIC Virtualization Extensions support the implementation of a GIC in a multiprocessor system that supports processor virtualization. This chapter includes a description of the programmers' model for the virtual interface control and virtual CPU interface registers.

#### Appendix A Pseudocode Index

Read this for an index to the pseudocode functions defined in this specification.

#### **Appendix B** Register Names

Read this for a description of the differences in the register names in earlier descriptions of the GIC architecture, and for an alphabetic index of the register names.

#### Appendix C Revisions

Read this for a description of the technical changes between released issues of this book.

Glossary Read this for definitions of some terms used in this book.

# Conventions

The following sections describe conventions that this book can use:

- General typographic conventions

- Signals

- Numbers

- Pseudocode descriptions.

# General typographic conventions

The typographical conventions are:

italic Introduces special terminology, denotes internal cross-references and citations, or

highlights an important note.

**bold** Denotes signal names, and is used for terms in descriptive lists, where appropriate.

monospace Used for assembler syntax descriptions, pseudocode, and source code examples.

Also used in the main text for instruction mnemonics and for references to other items appearing in assembler syntax descriptions, pseudocode, and source code examples.

SMALL CAPITALS Used for a few terms that have specific technical meanings, and are included in the

Glossary.

**Colored text** Indicates a link. This can be:

• a URL, for example, http://infocenter.arm.com

a cross-reference, that includes the page number of the referenced information if it is not on the current page, for example, *Distributor Control Register*, *GICD\_CTLR* on page 4-85

a link, to a chapter or appendix, or to a glossary entry, or to the section of the document that defines the colored term, for example *Banked register* or GICD CTLR.

# **Signals**

In general this specification does not define processor signals, but it does include some signal examples and recommendations. The signal conventions are:

**Signal level** The level of an asserted signal depends on whether the signal is active-HIGH or active-LOW. Asserted means:

HIGH for active-HIGH signals

• LOW for active-LOW signals.

**Lower-case n** At the start or end of a signal name denotes an active-LOW signal.

#### **Numbers**

Numbers are normally written in decimal. Binary numbers are preceded by 0b, and hexadecimal numbers by 0x. In both cases, the prefix and the associated value are written in a monospace font, for example 0xFFFF0000.

# **Pseudocode descriptions**

This specification uses a form of pseudocode to provide precise descriptions of the specified functionality. This pseudocode is written in a monospace font, and follows the conventions described in the ARM Architecture Reference Manual, ARMv7-A and ARMv7-R edition.

# **Additional reading**

This section lists relevant publications from ARM and third parties.

See the Infocenter, http://infocenter.arm.com, for access to ARM documentation.

# **ARM** publications

ARM Architecture Reference Manual, ARMv7-A and ARMv7-R edition (ARM DDI 0406), issue C or later.

# Other publications

The following books are referred to in this manual, or provide more information:

• JEDEC Solid State Technology Association, Standard Manufacture's Identification Code, JEP106.

# **Feedback**

ARM welcomes feedback on its documentation.

# Feedback on this specification

If you have comments on the content of this specification, send e-mail to errata@arm.com. Give:

- the title

- the number, ARM IHI 0048B.b

- the page numbers to which your comments apply

- a concise explanation of your comments.

ARM also welcomes general suggestions for additions and improvements.

# Chapter 1 **Introduction**

This chapter gives an overview of the GIC and information about the terminology used in this document. It contains the following sections:

- About the Generic Interrupt Controller architecture on page 1-14

- Security Extensions support on page 1-16

- Virtualization support on page 1-17

- *Terminology* on page 1-18.

# 1.1 About the Generic Interrupt Controller architecture

The Generic Interrupt Controller (GIC) architecture defines:

- · the architectural requirements for handling all interrupt sources for any processor connected to a GIC

- a common interrupt controller programming interface applicable to uniprocessor or multiprocessor systems.

| ——— Note |  |

|----------|--|

| Tiote    |  |

The architecture describes a GIC designed for use with one or more processors that comply with the ARM A and R architecture profiles. However the GIC architecture does not place any restrictions on the processors used with an implementation of the GIC.

The GIC is a centralized resource for supporting and managing interrupts in a system that includes at least one processor. It provides:

- registers for managing interrupt sources, interrupt behavior, and interrupt routing to one or more processors

- support for:

- the ARM architecture Security Extensions

- the ARM architecture Virtualization Extensions

- enabling, disabling, and generating processor interrupts from hardware (peripheral) interrupt sources

- Software-generated Interrupts (SGIs)

- interrupt masking and prioritization

- uniprocessor and multiprocessor environments

- wakeup events in power-management environments.

The GIC includes *interrupt grouping* functionality that supports:

- configuring each interrupt as either Group 0 or Group 1

- signaling Group 0 interrupts to the target processor using either the IRQ or the FIQ exception request

- signaling Group 1 interrupts to the target processor using the IRQ exception request only

- a unified scheme for handling the priority of Group 0 and Group 1 interrupts

- optional lockdown of the configuration of some Group 0 interrupts.

#### —— Note ——

- Interrupt grouping is present in all GICv2 implementations and in GICv1 implementations that include the GIC Security Extensions, see *Changes in version 2.0 of the Specification* on page 1-15.

- In many implementations the IRQ and FIQ interrupt requests correspond to the IRQ and FIQ asynchronous exceptions that are supported by all variants of the ARM architecture except the *Microcontroller profile* (M-profile). For more information about IRQ, FIQ, and asynchronous exceptions, see the *ARM Architecture Reference Manual, ARMv7-A and ARMv7-R edition*.

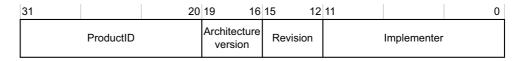

# 1.1.1 GIC architecture specification version

This specification defines version 2.0 of the GIC architecture (GICv2), and also describes version 1.0 of the architecture (GICv1).

The GIC architecture specification version is independent of the *rnpn* version, or major and minor revision description, used for ARM product releases.

# 1.1.2 Changes in version 2.0 of the Specification

Version 2.0 of the Architecture Specification contains the following changes and additions to version 1.0:

- 1. The addition of the optional GIC Virtualization Extensions, that support the implementation of the GIC in a system that supports processor virtualization. For more information, see *Virtualization support* on page 1-17.

- 2. A change to the architectural status of *interrupt grouping*. Interrupt grouping, and the ability to use FIQs to signal Group 0 interrupts, are provided:

- in all GICv2 implementations

- only as part of the optional Security Extensions in GICv1 implementations.

| —— Note ———                                       |                                                                 |

|---------------------------------------------------|-----------------------------------------------------------------|

| In version 1.0 of the Specification, interrupt gr | ouping is presented only as the classification of interrupts as |

| Secure or Non-secure, see item 7 of this list.    |                                                                 |

- 3. The addition of wakeup event support in power management environments. For more information, see *Power management*, *GIC v2* on page 2-31.

- 4. The addition of support for the save and restore of all GIC state, for power-down, or context switching, including virtual machine context switching in a system that supports virtualization. This means that some state that is read-only in GICv1 becomes read/write in GICv2. For more information, see *Preserving and restoring GIC state* on page 4-155.

- 5. The addition of an option to split interrupt completion into two stages, *Priority drop* and *interrupt deactivation*. For more information, see *Priority drop and interrupt deactivation* on page 3-38.

- 6. The addition of controls to disable the forwarding of legacy interrupt signals to a connected processor when forwarding of interrupts from the GIC to that processor is also disabled. For more information see *Interrupt signal bypass, and GICv2 bypass disable* on page 2-27.

- 7. Changes to the terminology used to describe the interrupt grouping features of the GICv1 Security Extensions, to clarify that these features can be used to implement functionality that is unrelated to the scope of the ARM Security Extensions present on an ARM processor.

| ——Note ———                                                                                        |

|---------------------------------------------------------------------------------------------------|

| As indicated in item 2, these features of the GICv1 Security Extensions are included in all GICv2 |

| implementations. That is, in GICv2 they are not part of the optional Security Extensions.         |

The terminology change includes renaming the Interrupt Security Registers to Interrupt Group Registers. These registers separate interrupts into two groups, Group 0 and Group 1. In specific contexts, typically when a GIC that implements the GIC Security Extensions is connected to an ARM processor that implements the processor Security Extensions, Group 0 interrupts are Secure interrupts and Group 1 interrupts are Non-secure interrupts. For more information, see *Security Extensions support* on page 1-16.

# 1.2 Security Extensions support

The ARM processor Security Extensions are an optional extension to the ARMv7-A architecture profile. This means it is IMPLEMENTATION DEFINED whether an ARMv7-A implementation includes the Security Extensions. The ARM Security Extensions facilitate the development of secure applications by:

- integrating hardware security features into the architecture

- providing Secure virtual memory space that is accessed by memory accesses in the Secure state

- providing Non-secure virtual memory space that is accessed by memory accesses in the Non-secure state.

See Processor security state and Secure and Non-secure GIC accesses on page 1-20 for more information.

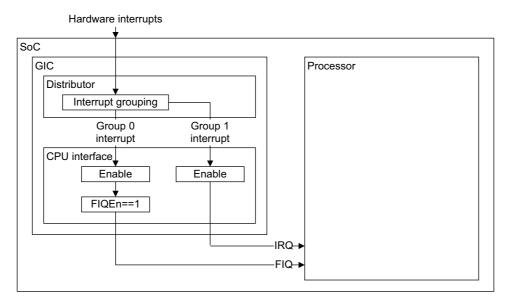

When a GIC that implements the GIC Security Extensions is connected to a processor that implements the ARM Security Extensions:

- Group 0 interrupts are Secure interrupts, and Group 1 interrupts are Non-secure interrupts.

- The behavior of processor accesses to registers in the GIC depends on whether the access is Secure or Non-secure, see *Processor security state and Secure and Non-secure GIC accesses* on page 1-20.

Except where this document explicitly indicates otherwise, when accessing GIC registers:

- a Non-secure read of a register field holding state information for a Secure interrupt returns zero

- the GIC ignores any Non-secure write to a register field holding state information for a Secure interrupt.

Non-secure accesses can only read or write information corresponding to Non-secure interrupts. Secure accesses can read or write information corresponding to both Non-secure and Secure interrupts.

- Secure system software individually defines each implemented interrupt as either Secure or Non-secure.

- A Non-secure interrupt signals an IRQ interrupt request to a target processor.

- A Secure interrupt can signal either an IRQ or an FIQ interrupt request to a target processor.

- Secure software can manage interrupt sources securely without the possibility of interference from Non-secure software. See Controlling Secure and Non-secure interrupts independently on page 3-69 for more information.

Secure systems are backwards-compatible with software written for systems without the Security Extensions. See *Supporting IRQs and FIQs when not using the processor Security Extensions* on page 3-70 for more information.

# 1.3 Virtualization support

The ARM processor Virtualization Extensions are optional extensions to the ARMv7-A architecture profile. This means it is IMPLEMENTATION DEFINED whether an ARMv7-A implementation includes the Virtualization Extensions.

The processor Virtualization Extensions provide hardware support for virtualizing the Non-secure state of an VMSAv7 implementation. The extensions support system use of a virtual machine monitor, known as the hypervisor, to switch guest operating systems.

Whether implemented in a uniprocessor or in a multiprocessor system, the processor Virtualization Extensions support running multiple virtual machines on a single processor.

Interrupt handling is a major consideration in a virtualization implementation. The hypervisor can either handle a physical interrupt itself, or generate a corresponding virtual interrupt that is signaled to a virtual machine. It is also possible for the hypervisor to generate virtual interrupts that do not correspond to physical interrupts.

GICv2 extends the GIC architecture to include the GIC Virtualization Extensions. These extensions support the handling of virtual interrupts, in addition to physical interrupts, in a system that supports processor virtualization. An example of such a system is one where a GIC is integrated with processors that implement the ARM processor Virtualization Extensions. The GIC Virtualization Extensions provide mechanisms to minimize the hypervisor overhead of routing interrupts to virtual machines. See Chapter 5 GIC Support for Virtualization for more information.

#### — Note —

- A processor that implements the ARM Virtualization Extensions must also implement the ARM Security Extensions.

- A GIC that implements the GIC Virtualization Extensions is not required to implement the GIC Security Extensions.

#### 1.4 **Terminology**

The following sections define architectural terms used in this specification:

- Interrupt states

- Interrupt types

- Models for handling interrupts on page 1-19

- Spurious interrupts on page 1-20

- Processor security state and Secure and Non-secure GIC accesses on page 1-20

- Banking on page 1-20.

See also GIC register names on page 4-74.

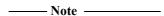

#### 1.4.1 Interrupt states

The following states apply at each interface between the GIC and a connected processor:

Inactive An interrupt that is not active or pending.

**Pending** An interrupt from a source to the GIC that is recognized as asserted in hardware, or

generated by software, and is waiting to be serviced by a target processor.

Active An interrupt from a source to the GIC that has been acknowledged by a processor, and is

being serviced but has not completed.

A processor is servicing the interrupt and the GIC has a pending interrupt from the same Active and pending

source

#### 1.4.2 Interrupt types

A device that implements this GIC architecture can manage the following types of interrupt:

Peripheral interrupt This is an interrupt asserted by a signal to the GIC. The GIC architecture defines the following types of peripheral interrupt:

#### **Private Peripheral Interrupt (PPI)**

This is a peripheral interrupt that is specific to a single processor.

#### **Shared Peripheral Interrupt (SPI)**

This is a peripheral interrupt that the Distributor can route to any of a specified combination of processors.

Each peripheral interrupt is either:

#### Edge-triggered

This is an interrupt that is asserted on detection of a rising edge of an interrupt signal and then, regardless of the state of the signal, remains asserted until it is cleared by the conditions defined by this specification.

#### Level-sensitive

This is an interrupt that is asserted whenever the interrupt signal level is active, and deasserted whenever the level is not active.

| Note                                                                                         |

|----------------------------------------------------------------------------------------------|

| While a level-sensitive interrupt is asserted its state in the GIC is pending, or active and |

| pending. If the peripheral deasserts the interrupt signal for any reason the GIC removes the |

| pending state from the interrupt. For more information see Interrupt handling state machine  |

| on page 3-41.                                                                                |

#### Software-generated interrupt (SGI)

This is an interrupt generated by software writing to a GICD\_SGIR register in the GIC. The system uses SGIs for interprocessor communication.

An SGI has edge-triggered properties. The software triggering of the interrupt is equivalent to the edge transition of the interrupt request signal.

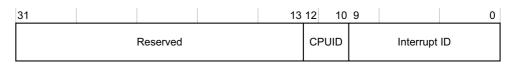

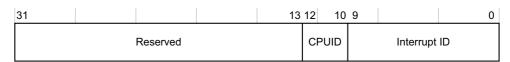

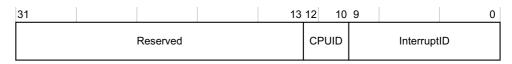

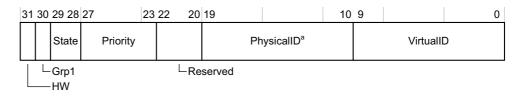

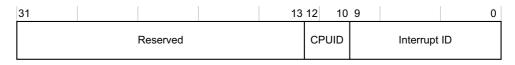

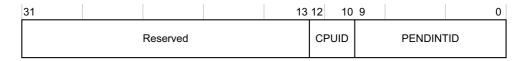

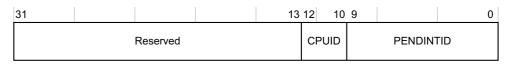

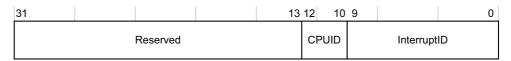

When an SGI occurs in a multiprocessor implementation, the CPUID field in the Interrupt Acknowledge Register, GICC\_IAR, or the Aliased Interrupt Acknowledge Register, GICC\_AIAR, identifies the processor that requested the interrupt.

In an implementation that includes the GIC Virtualization Extensions:

- when an SGI occurs, management registers in the GIC virtualization Extensions enable the requesting processor to be reported to the Guest OS, as required by the GIC specifications

- by writing to the management registers in the GIC Virtualization Extensions, a hypervisor can generate a virtual interrupt that appears to a virtual machine as an SGI.

See *Software-generated interrupts* on page 5-165 and *List Registers, GICH\_LRn* on page 5-176 for more information.

#### Virtual interrupt

In a GIC that implements the GIC Virtualization Extensions, an interrupt that targets a virtual machine running on a processor, and is typically signaled to the processor by the connected virtual CPU interface. For more information, see *About GIC partitioning* on page 2-22.

#### Maintenance interrupt

In a GIC that implements the GIC Virtualization Extensions, a level-sensitive interrupt that is used to signal key events, such as a particular group of interrupts becoming enabled or disabled. See *Maintenance interrupts* on page 5-164 for more information.

#### 1.4.3 Models for handling interrupts

\_\_\_\_\_ Note \_\_\_\_\_

When describing the GIC interrupt handling models, the terms 1-N and N-N do not correspond to the mathematical uses of the terms 1:N and N:N.

In a multiprocessor implementation, there are two models for handling interrupts:

1-N model

Only one processor handles this interrupt. The system must implement a mechanism to determine which processor handles an interrupt that is programmed to target more than one processor.

\_\_\_\_\_ Note \_\_\_\_\_

- The ARM GIC architecture does not guarantee that a 1-N interrupt is presented to:

- all processors listed in the target processor list

- an enabled interface, where at least one interface is enabled.

- A 1-N interrupt might be presented to an interface where the processor has masked the interrupt event, see *Implications of the 1-N model* on page 3-41.

N-N model

All processors receive the interrupt independently. When a processor acknowledges the interrupt, the interrupt pending state is cleared only for that processor. The interrupt remains pending for the other processors.

See Handling different interrupt types in a multiprocessor system on page 3-35 for more information.

#### 1.4.4 Spurious interrupts

It is possible that an interrupt that the GIC has signaled to a processor is no longer required. If this happens, when the processor acknowledges the interrupt, the GIC returns a special Interrupt ID that identifies the interrupt as a *spurious interrupt*. Example reasons for spurious interrupts are:

- prior to the processor acknowledging an interrupt:

- software changes the priority of the interrupt

- software disables the interrupt

- software changes the processor that the interrupt targets

- for a 1-N interrupt, another target processor has previously acknowledged that interrupt.

### 1.4.5 Processor security state and Secure and Non-secure GIC accesses

A processor that implements the ARM Security Extensions has a security state, either Secure or Non-secure:

- a processor in Non-secure state can make only Non-secure accesses to a GIC

- a processor in Secure state can make both Secure and Non-secure accesses to a GIC

- software running in Non-secure state is described as Non-secure software

- software running in Secure state is described as Secure software.

For more information about the implementation of the Security Extensions on a processor see the ARM Architecture Reference Manual, ARMv7-A and ARMv7-R edition.

A multiprocessor system with a GIC that implements the Security Extensions might include one or more processors that do not implement the Security Extensions. Such a processor is implemented so that either:

- it makes only Secure accesses to the GIC, meaning any software running on the processor is Secure software that can only make Secure accesses to the GIC

- it makes only Non-secure accesses to the GIC, meaning any software running on the processor is Non-secure software.

#### 1.4.6 Banking

Banking has a special meaning in ARM architectural specifications:

## Interrupt banking

In a multiprocessor implementation, for PPIs and SGIs, the GIC can have multiple interrupts with the same interrupt ID. Such an interrupt is called a *banked interrupt*, and is identified uniquely by the combination of its interrupt ID and its associated CPU interface. For more information see *Interrupt IDs* on page 2-24.

#### Register banking

Register banking refers to implementing multiple copies of a register at the same address. This occurs:

- in a multiprocessor implementation, to provide separate copies for each processor of registers corresponding to banked interrupts

- in a GIC that implements the Security Extensions, to provide separate Secure and Non-secure copies of some registers.

For more information see Register banking on page 4-77.

# Chapter 2 **GIC Partitioning**

This chapter describes the architectural partitioning of the major GIC interfaces and components, and introduces the functionality of the major GIC components, the *Distributor* and the *CPU interfaces*. It contains the following sections:

- About GIC partitioning on page 2-22

- The Distributor on page 2-24

- *CPU interfaces* on page 2-26.

# 2.1 About GIC partitioning

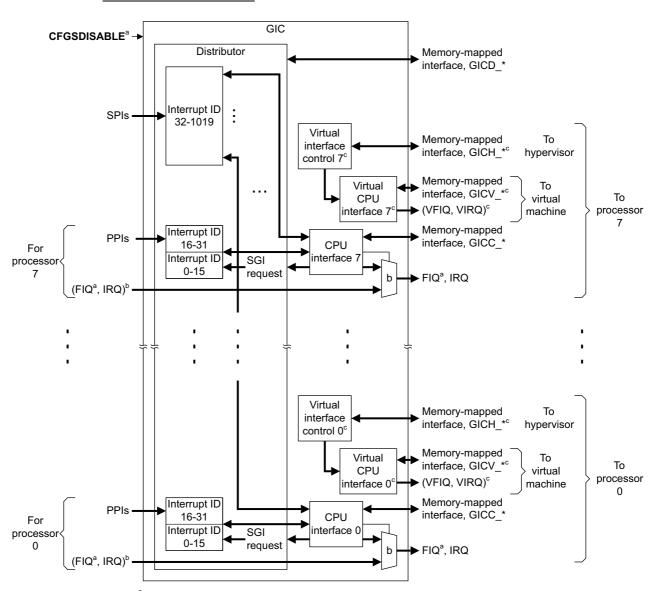

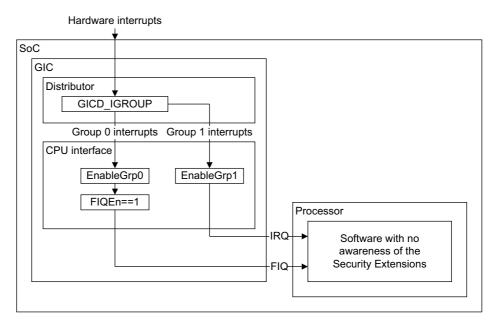

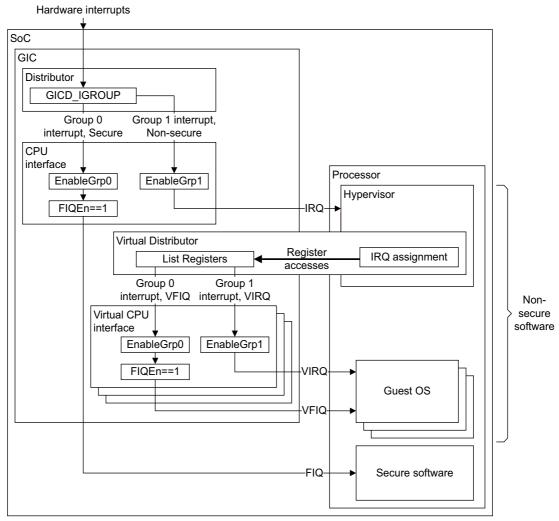

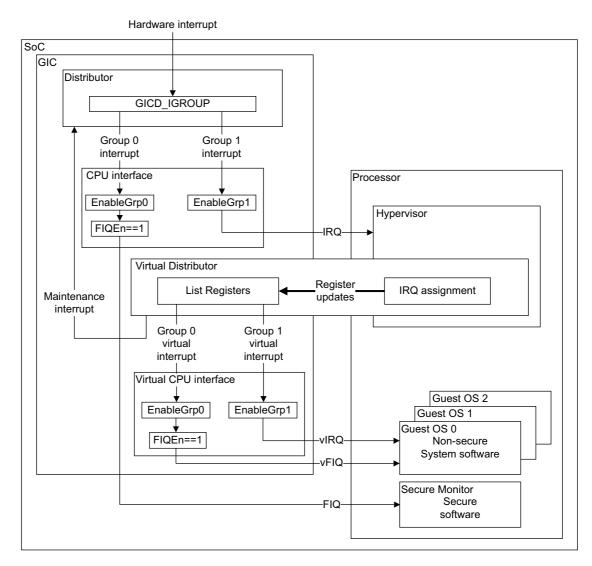

The GIC architecture splits logically into a Distributor block and one or more CPU interface blocks. The GIC Virtualization Extensions add one or more virtual CPU interfaces to the GIC. Therefore, as Figure 2-1 on page 2-23 shows, the logical partitioning of the GIC is as follows:

**Distributor** The Distributor block performs interrupt prioritization and distribution to the CPU interface

blocks that connect to the processors in the system.

The Distributor block registers are identified by the GICD prefix.

**CPU interfaces** Each CPU interface block performs priority masking and preemption handling for a

connected processor in the system.

CPU interface block registers are identified by the GICC\_ prefix.

When describing a GIC that includes the GIC Virtualization Extensions, a CPU interface is sometimes called a *physical CPU interface*, to avoid possible confusion with a virtual CPU

interface.

#### Virtual CPU interfaces

The GIC Virtualization Extensions add a virtual CPU interface for each processor in the system. Each virtual CPU interface is partitioned into the following blocks:

#### Virtual interface control

The main component of the virtual interface control block is the GIC virtual interface control registers, that include a list of active and pending virtual interrupts for the current virtual machine on the connected processor. Typically, these registers are managed by the hypervisor that is running on that processor. Virtual interface control block registers are identified by the GICH prefix.

#### Virtual CPU interface

Each virtual CPU interface block provides physical signaling of virtual interrupts to the connected processor. The ARM processor Virtualization Extensions signal these interrupts to the current virtual machine on that processor. The GIC virtual CPU interface registers, accessed by the virtual machine, provide interrupt control and status information for the virtual interrupts. The format of these registers is similar to the format of the physical CPU interface registers.

Virtual CPU interface block registers are identified by the GICV\_prefix.

| —— Note ———                                                                             |

|-----------------------------------------------------------------------------------------|

| The virtual CPU interface does not support the power management functionality described |

| in Power management, GIC v2 on page 2-31.                                               |

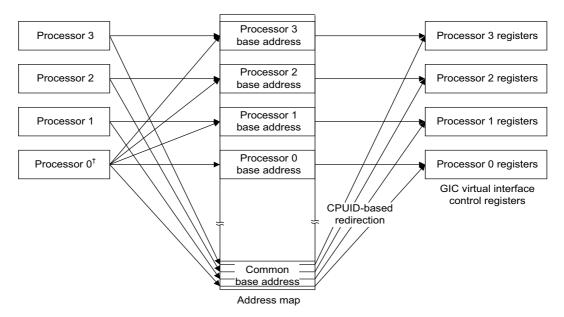

A GIC can implement up to eight CPU interfaces, numbered from 0-7. In a GIC that implements the GIC Virtualization Extensions, virtual CPU interface numbering corresponds to the CPU interface numbering, so that CPU interface 0 and virtual CPU interface 0 connect to the same processor.

This model supports implementation of the GIC in uniprocessing or multiprocessing environments, and the GIC Virtualization Extensions extend that support to processors that support virtualization, in which, in Non-secure state:

- A Guest OS runs on a virtual machine

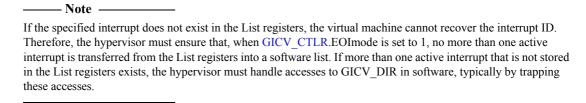

- A hypervisor is responsible for switching between virtual machines. This switching includes switching the state held in the GIC virtual interface control registers.

Each block provides part of the GIC programmers' model, and:

- the programmers' model is generally the same for each implemented CPU interface.

- the programmers' model for a virtual CPU interface is generally the same as the programmers' model for a physical CPU interface.

#### — Note —

- The partitioning of the GIC described in this section is an architectural abstraction. Whether these blocks are implemented separately or combined is IMPLEMENTATION SPECIFIC.

- In a GIC that implements the GIC Security Extensions in a multiprocessor system, a CPU interface can be implemented so that it receives:

- both Secure and Non-secure accesses

- only Secure accesses

- only Non-secure accesses.

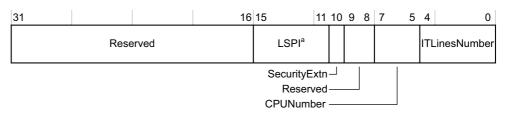

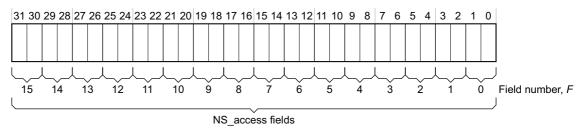

<sup>&</sup>lt;sup>a</sup> In GICv1, applies only if Security Extensions are implemented

Figure 2-1 GIC logical partitioning

The remainder of this chapter, and Chapter 3 *Interrupt Handling and Prioritization* and Chapter 4 *Programmers' Model*, describe the GIC without the GIC Virtualization Extensions. Chapter 5 *GIC Support for Virtualization* describes the features added by the GIC Virtualization Extensions.

<sup>&</sup>lt;sup>b</sup>Optional input and bypass multiplexer, see text

<sup>&</sup>lt;sup>c</sup> Applies only to GICv2 with Virtualization Extensions

### 2.2 The Distributor

The Distributor centralizes all interrupt sources, determines the priority of each interrupt, and for each CPU interface forwards the interrupt with the highest priority to the interface, for priority masking and preemption handling.

The Distributor provides a programming interface for:

- Globally enabling the forwarding of interrupts to the CPU interfaces.

- Enabling or disabling each interrupt.

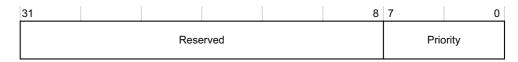

- Setting the priority level of each interrupt.

- Setting the target processor list of each interrupt.

- Setting each peripheral interrupt to be level-sensitive or edge-triggered.

- Setting each interrupt as either Group 0 or Group 1.

| Note - |  |

|--------|--|

|--------|--|

For GICv1, setting interrupts as Group 0 or Group 1 is possible only when the implementation includes the GIC Security Extensions.

• Forwarding an SGI to one or more target processors.

In addition, the Distributor provides:

- visibility of the state of each interrupt

- a mechanism for software to set or clear the pending state of a peripheral interrupt.

#### 2.2.1 Interrupt IDs

Interrupts from sources are identified using *ID numbers*. Each CPU interface can see up to 1020 interrupts. The banking of SPIs and PPIs increases the total number of interrupts supported by the Distributor.

The GIC assigns interrupt ID numbers ID0-ID1019 as follows:

- Interrupt numbers ID32-ID1019 are used for SPIs.

- Interrupt numbers ID0-ID31 are used for interrupts that are private to a CPU interface. These interrupts are banked in the Distributor.

A banked interrupt is one where the Distributor can have multiple interrupts with the same ID. A banked interrupt is identified uniquely by its ID number and its associated CPU interface number. Of the banked interrupt IDs:

- ID0-ID15 are used for SGIs

- ID16-ID31 are used for PPIs

In a multiprocessor system:

- A PPI is forwarded to a particular CPU interface, and is private to that interface. In prioritizing

interrupts for a CPU interface the Distributor does not consider PPIs that relate to other interfaces.

- Each connected processor issues an SGI by writing to the GICD\_SGIR in the Distributor. Each write can generate SGIs with the same ID that target multiple processors.

In the Distributor, an SGI is identified uniquely by the combination of its interrupt number, ID0-ID15, the target processor ID, CPUID0-CPUID7, and the *processor source ID*, CPUID0-CPUID7, of the processor that issued the SGI. When the CPU interface communicates the interrupt ID to a targeted processor, it also provides the processor source ID, so that the targeted processor can uniquely identify the SGI.

SGI banking means the GIC can handle multiple SGIs simultaneously, without resource conflicts. The Distributor ignores any write to the GICD\_SGIR that is not from a processor that is connected to one of the CPU interfaces. How the Distributor determines the processor source ID of a processor writing to the GICD\_SGIR is IMPLEMENTATION SPECIFIC.

In a uniprocessor system, there is no distinction between shared and private interrupts, because all interrupts are visible to the processor. In this case the processor source ID value is 0.

• Interrupt numbers ID1020-ID1023 are reserved for special purposes, see *Special interrupt numbers* on page 3-43.

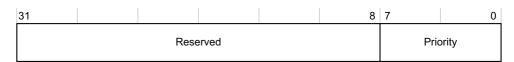

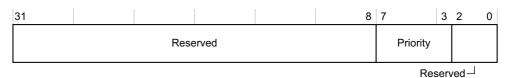

System software sets the priority of each interrupt. This priority is independent of the interrupt ID number.

In any system that implements the ARM Security Extensions, to support a consistent model for message passing between processors, ARM strongly recommends that all processors reserve:

- ID0-ID7 for Non-secure interrupts

- ID8-ID15 for Secure interrupts.

# 2.3 CPU interfaces

Each CPU interface block provides the interface for a processor that is connected to the GIC. Each CPU interface provides a programming interface for:

- enabling the signaling of interrupt requests to the processor

- acknowledging an interrupt

- indicating completion of the processing of an interrupt

- setting an interrupt priority mask for the processor

- defining the preemption policy for the processor

- determining the highest priority pending interrupt for the processor.

When enabled, a CPU interface takes the highest priority pending interrupt for its connected processor and determines whether the interrupt has *sufficient priority* for it to signal the interrupt request to the processor. To determine whether to signal the interrupt request to the processor, the CPU interface considers the interrupt priority mask and the preemption settings for the processor. At any time, the connected processor can read the priority of its highest priority active interrupt from its GICC\_HPPIR, a CPU interface register.

The mechanism for signaling an interrupt to the processor is IMPLEMENTATION DEFINED.

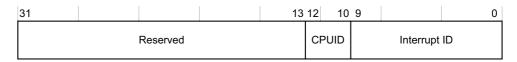

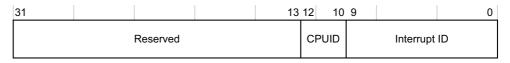

The processor acknowledges the interrupt request by reading the CPU interface Interrupt Acknowledge Register. This read returns one of:

- The ID number of the highest priority pending interrupt, if that interrupt is of sufficient priority for it to be signaled to the processor. This is the normal response to an interrupt acknowledge.

- Exceptionally, an ID number that indicates a *spurious interrupt*.

When the processor acknowledges the interrupt at the CPU interface, the Distributor changes the status of the interrupt from pending to either active, or active and pending. At this point the CPU interface can signal another interrupt to the processor, to preempt interrupts that are active on the processor. If there is no pending interrupt with sufficient priority for signaling to the processor, the interface deasserts the interrupt request signal to the processor.

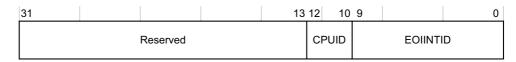

When the interrupt handler on the processor has completed the processing of an interrupt, it writes to the CPU interface to indicate interrupt completion. There are two stages to interrupt completion:

- priority drop, meaning the priority of the processed interrupt can no longer prevent the signaling of another interrupt to the processor

- interrupt deactivation, meaning the Distributor removes the active state of the interrupt.

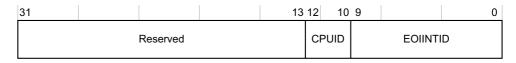

In a GICv1 implementation, these two stages always happen together, when the processor writes to the CPU interface End of Interrupt register.

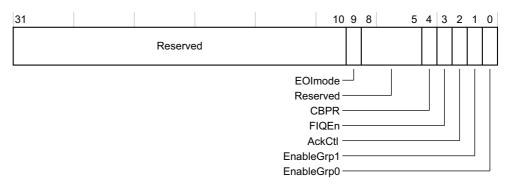

In a GICv2 implementation, the GICC CTLR.EOImode bit determines whether:

- the two stages happen together, when the processor writes to the CPU interface End of Interrupt register

- the two stages are separated, so that:

- priority drop happens when the processor writes to the CPU interface End of Interrupt register

- interrupt deactivation happens later, when the processor writes to the CPU interface Deactivate Interrupt register.

For more information, see *Priority drop and interrupt deactivation* on page 3-38.

#### 2.3.1 Interrupt signal bypass, and GICv2 bypass disable

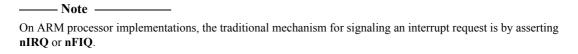

In all GIC implementations, a CPU interface optionally includes interrupt signal bypass, so that, when the signaling of an interrupt by the interface is disabled, a system legacy interrupt signal is passed to the interrupt request input on the processor, bypassing the GIC functionality.

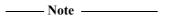

Figure 2-2 shows the implementation of interrupt signal bypass on a GICv1 implementation that does not include the GIC Security Extensions.

Figure 2-2 Interrupt signal bypass, GICv1 without Security Extensions

Figure 2-2 shows the simplest implementation of interrupt signal bypass. In other GIC implementations, interrupt signal bypass is more complicated:

- A GICv1 implementation that includes the GIC Security Extensions supports interrupt grouping, and the use of FIQ interrupts to signal Group 0 interrupts. *Interrupt bypass, GICv1 with GIC Security Extensions* describes the implementation of interrupt bypass on such an implementation.

- If a GICv2 implementation interrupt supports signal bypass, it uses the same model as a GICv1 implementation that includes the GIC Security Extensions, but must also provide disable bits for the interrupt signal bypass operation. For more information see GICv2 interrupt bypass, with bypass disable on page 2-28.

Many ARM processors, including processors that implement the ARMv7-A or ARMv7-R architecture profiles, implement two active-LOW interrupt request signals, **nIRQ** and **nFIQ**. However, this GIC architecture specification describes only the logic of the interrupt request signals, not the physical signaling of interrupts to a connected processor. Therefore, it describes two active-HIGH interrupt requests, IRQ and FIQ.

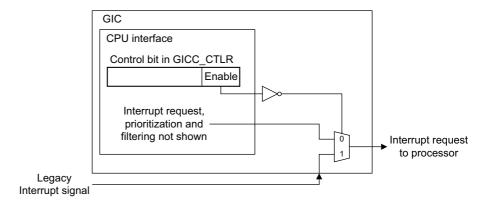

## Interrupt bypass, GICv1 with GIC Security Extensions

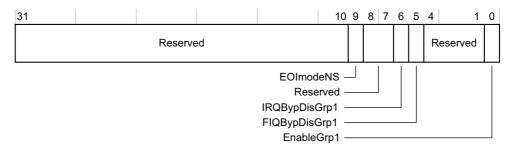

When a GIC implementation supports interrupt grouping, a CPU interface can provide two interrupt exception request outputs, IRQ and FIQ. It always uses the IRQ output to signal Group 1 interrupts, but can use the FIQ output to signal Group 0 interrupts. In such an implementation, the CPU interface can include interrupt signal bypass for both interrupt signals. For this case, Table 2-1 on page 2-28 shows how GICC\_CTLR controls the GIC interrupt outputs.

Table 2-1 Interrupt signal bypass behavior, GICv1 with Security Extensions

| GICC_CTLR register bits |            |            | GIC interrupt outputs       |                             |  |

|-------------------------|------------|------------|-----------------------------|-----------------------------|--|

| FIQEn                   | EnableGrp0 | EnableGrp1 | IRQ request behavior        | FIQ request behavior        |  |

| 0                       | 0          | 0          | Bypass                      | Bypass                      |  |

|                         |            | 1          | Driven by GIC CPU interface | Bypass                      |  |

|                         | 1          | 0          | Driven by GIC CPU interface | Bypass                      |  |

|                         |            | 1          | Driven by GIC CPU interface | Bypass                      |  |

| 1                       | 0          | 0          | Bypass                      | Bypass                      |  |

|                         |            | 1          | Driven by GIC CPU interface | Bypass                      |  |

|                         | 1          | 0          | Bypass                      | Driven by GIC CPU interface |  |

|                         |            | 1          | Driven by GIC CPU interface | Driven by GIC CPU interface |  |

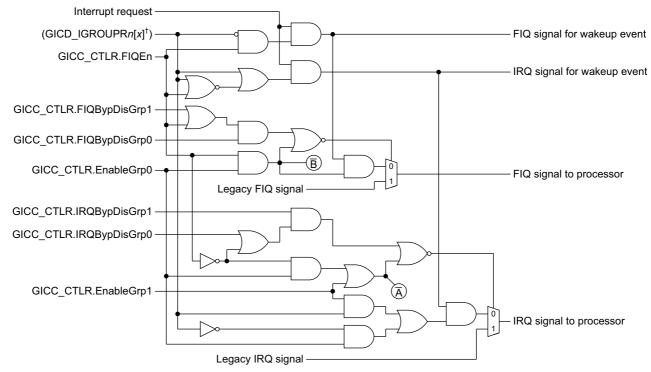

For such an implementation, Figure 2-3 shows the signaling of the Group 0 and Group 1 interrupts.

Figure 2-3 GICv1 Group 0 and Group 1 interrupt signaling, with interrupt signal bypass

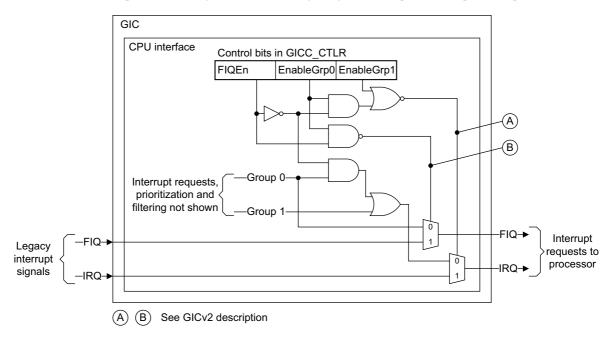

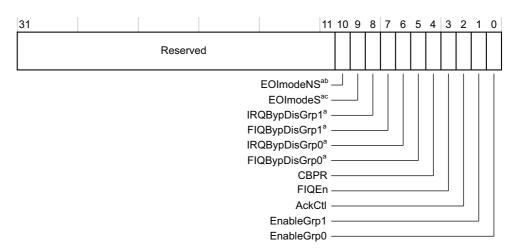

### GICv2 interrupt bypass, with bypass disable

When a CPU interface in a GICv2 implementation includes interrupt signal bypass, it:

- implements the bypass scheme described in *Interrupt bypass, GICv1 with GIC Security Extensions* on page 2-27

- in addition, must implement GICC\_CTLR control bits that disable the interrupt signal bypass functionality.

When not being driven by the CPU interface, each interrupt output signal can be deasserted rather than being driven by the legacy interrupt input. This behavior is controlled by the GICC\_CTLR bypass disable bits:

- FIQBypDisGrp0

- FIQBypDisGrp1

- IRQBypDisGrp0

- IRQBypDisGrp1.

Figure 2-4 shows the control logic of the signaling of interrupts by a CPU interface. *Power management, GIC v2* on page 2-31 gives more information about the wakeup event signals shown in Figure 2-4.

- † Values of *n* and *x* correspond to the requested interrupt

- $(\overline{A})$  is the inverse of  $(\overline{A})$  in the GICv1 implementation that supports interrupt grouping

- $(\overline{B})$  is the inverse of  $(\overline{B})$  in the GICv1 implementation that supports interrupt grouping

## Figure 2-4 GICv2 interrupt bypass logic, with bypass disable

Exception generation pseudocode on page 3-64 also describes this interrupt signaling.

Table 2-2 on page 2-30 shows how, when a CPU interface might signal an IRQ request to a connected processor, bits in GICC\_CTLR, and whether the IRQ request is Group 0 or Group 1, determine the IRQ signaling by the interface. In the IRQ request signaling behavior column of this table:

**Bypass** Indicates that the IRQ signal to the processor is driven by the legacy IRQ signal.

**Deasserted** Indicates that the IRQ signal to the processor is deasserted.

**Driven by GIC** Indicates that the IRQ signal to the processor is driven by the GIC CPU interface logic.

Table 2-2 IRQ request behavior, GICv2

| GICC_CTLR register bits IRQ for IRQ request sign |            |       |               |               |           | IRQ request signaling |

|--------------------------------------------------|------------|-------|---------------|---------------|-----------|-----------------------|

| EnableGrp1                                       | EnableGrp0 | FIQEn | IRQBypDisGrp1 | IRQBypDisGrp0 | signaling | behavior              |

| 0                                                | 0          | 0     | 0             | x             | x         | Bypass                |

| 0                                                | 0          | 0     | 1             | x             | х         | Deasserted            |

| 0                                                | 0          | 1     | 0             | x             | х         | Bypass                |

| 0                                                | 0          | 1     | 1             | 0             | X         | Bypass                |

| 0                                                | 0          | 1     | 1             | 1             | х         | Deasserted            |

| 0                                                | 1          | 0     | x             | x             | Group 0   | Driven by GIC         |

| 0                                                | 1          | 0     | x             | x             | Group 1   | Deasserted            |

| 0                                                | 1          | 1     | 0             | х             | X         | Bypass                |

| 0                                                | 1          | 1     | 1             | 0             | х         | Bypass                |

| 0                                                | 1          | 1     | 1             | 1             | X         | Deasserted            |

| 1                                                | 0          | X     | x             | x             | Group 0   | Deasserted            |

| 1                                                | 0          | X     | x             | x             | Group 1   | Driven by GIC         |

| 1                                                | 1          | 0     | x             | x             | X         | Driven by GIC         |

| 1                                                | 1          | 1     | x             | x             | Group 0   | Deasserted            |

| 1                                                | 1          | 1     | x             | x             | Group 1   | Driven by GIC         |

Table 2-3 shows how, when a CPU interface might signal an FIQ request to a connected processor, bits in GICC\_CTLR the FIQ signaling by the interface:

Table 2-3 FIQ request behavior, GICv2

| GICC_CTLR register bits |       |               |               | EIO request signaling behavior      |

|-------------------------|-------|---------------|---------------|-------------------------------------|

| EnableGrp0              | FIQEn | FIQBypDisGrp0 | FIQBypDisGrp1 | FIQ request signaling behavior      |

| 0                       | 0     | 0             | x             | Bypass, driven by legacy FIQ signal |

| 0                       | 0     | 1             | 0             | Bypass, driven by legacy FIQ signal |

| 0                       | 0     | 1             | 1             | FIQ interrupt output deasserted     |

| 0                       | 1     | 0             | x             | Bypass, driven by legacy FIQ signal |

| 0                       | 1     | 1             | x             | FIQ interrupt output deasserted     |

| 1                       | 0     | 0             | x             | Bypass, driven by legacy FIQ signal |

| 1                       | 0     | 1             | 0             | Bypass, driven by legacy FIQ signal |

| 1                       | 0     | 1             | 1             | FIQ interrupt output deasserted     |

| 1                       | 1     | X             | х             | Driven by GIC CPU interface         |

# 2.3.2 Power management, GIC v2

The GICv2 architecture supports wakeup events in implementations that require power management.

As shown in Figure 2-4 on page 2-29, the GICv2 interrupt bypass logic described in *GICv2 interrupt bypass, with bypass disable* on page 2-28 includes signals that can be used as wakeup signals to a system power controller. These signals are available even when both interrupt signaling by the GIC, and interrupt bypass, are disabled.

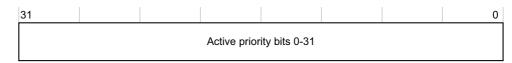

In addition, the GICC\_APRn registers provide support for preserving and restoring state in power-management applications. However, to ensure that Non-secure accesses do not interfere with Secure operation, Secure and Non-secure copies of these registers are provided.

2 GIC Partitioning 2.3 CPU interfaces

# Chapter 3

# **Interrupt Handling and Prioritization**

This chapter describes the requirements for interrupt handling and prioritization in the GIC. It contains the following sections:

- About interrupt handling and prioritization on page 3-34

- General handling of interrupts on page 3-37

- Interrupt prioritization on page 3-44

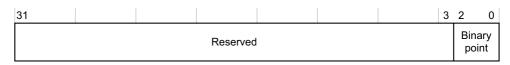

- The effect of interrupt grouping on interrupt handling on page 3-48

- *Interrupt grouping and interrupt prioritization* on page 3-53

- Additional features of the GIC Security Extensions on page 3-59

- Pseudocode details of interrupt handling and prioritization on page 3-61

- The effect of the Virtualization Extensions on interrupt handling on page 3-67

- Example GIC usage models on page 3-68.

# 3.1 About interrupt handling and prioritization

The following subsections give more information about the interrupts supported by a GIC, and how a connected processor must determine the range of interrupt IDs supported by the GIC:

- Handling different interrupt types in a multiprocessor system on page 3-35

- *Identifying the supported interrupts* on page 3-35.

The remainder of the chapter describes interrupt handling and prioritization.

#### Interrupt handling describes:

- how the GIC recognizes interrupts

- how software can program the GIC to configure and control interrupts

- the state machine the GIC maintains for each interrupt on each CPU interface

- how the exception model of a processor interacts with the GIC.

#### Prioritization describes:

- the configuration and control of interrupt priority

- the order of execution of pending interrupts

- the determination of when interrupts are visible to a target processor, including:

- interrupt priority masking

- priority grouping

- preemption of an active interrupt.

The following sections describe interrupt handling and prioritization:

- *General handling of interrupts* on page 3-37

- Interrupt prioritization on page 3-44.

The GIC architecture supports uniprocessor and multiprocessor systems:

- in a uniprocessor system the GIC has a single processor interface, the CPU interface

- in a multiprocessor system the GIC has a CPU interface for each connected processor.

In either a uniprocessor or a multiprocessor system, a GIC implementation can include the GIC Security Extensions. The GIC Security Extensions:

- recognize that a connected processor that implements the ARM Security Extensions makes either Secure

accesses or Non-secure accesses to the GIC registers

- implement the GIC registers to take account of Secure and Non-secure accesses, so that:

- some registers are *banked*, to provide separate Secure and Non-secure copies

- some registers are Secure, meaning they are only accessible using Secure accesses

- the remaining registers are *Common*, meaning they are accessible by Secure and Non-secure accesses.

- use the GIC interrupt grouping feature to support the handling of Secure and Non-secure interrupts, in which

case:

- Group 0 interrupts are Secure interrupts

- Group 1 interrupts are Non-secure interrupts.

- in a multiprocessor system, might implement the GIC Security Extensions on only some of its CPU interfaces.

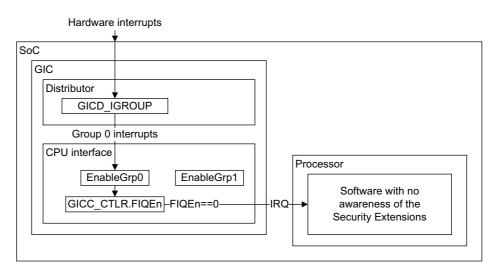

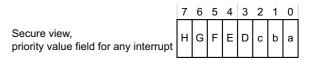

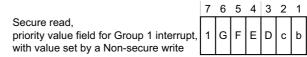

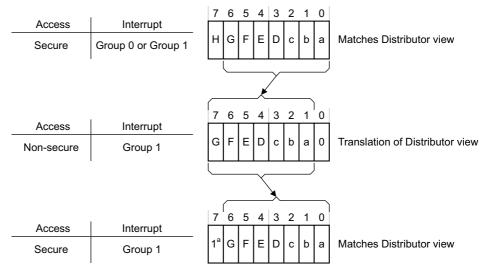

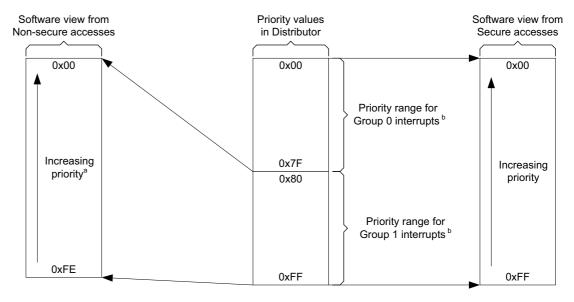

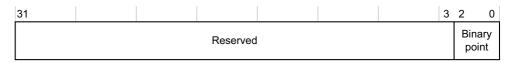

Except for a GICv1 implementation that does not include the GIC Security Extensions, all implementations of the GIC architecture support *interrupt grouping*. With interrupt grouping: